## Performance Evaluation of a 4-bit Full Adder under power, Thermal, and Hardware Constraints Using Simulation Technique

Dr. C. Aruna Bala<sup>1</sup>, P. Vani<sup>2</sup>, B. Anitha<sup>3</sup>, K. Thrisha<sup>4</sup>, K. Arun Teja<sup>5</sup>, M. Harish<sup>6</sup>

<sup>1</sup>Research supervisor, Assistant professor, Dept., of ECE, ALTS, Ananthapuram

<sup>2,3,4,5,6</sup> UG Scholar Dept., of ECE

### Article Info

Received: 22-02-2025

Revised: 22 -03-2025

Accepted: 08-04-2025

Published:19/04/2025

### ABSTRACT

Energy shortages pose a significant challenge in many developing countries, driving the need for energy-efficient digital circuits. This study presents the design and implementation of a low-power 4-bit full adder using multiple FPGA families, specifically Spartan-7 and Zynq, within the Xilinx Vivado framework. The proposed design integrates power-efficient techniques such as power gating, clock gating, and voltage scaling to minimize energy consumption while maintaining high performance. Special emphasis is placed on analyzing temperature effects, power dissipation, and overall circuit efficiency to enhance reliability and sustainability. Through extensive simulations and hardware implementation, the study demonstrates the viability of energy-conscious FPGA-based arithmetic circuits for modern communication systems. The results indicate substantial energy savings, reinforcing the importance of optimizing hardware utilization in digital design. This research contributes to the advancement of eco-friendly electronic devices, paving the way for more sustainable and energy-efficient communication hardware solutions.

**Keywords:** Energy efficiency, FPGA, 4-bit full adder, Xilinx Vivado, power gating, clock gating, voltage scaling, power dissipation, temperature analysis, digital circuits, low-power design, Spartan-7, Zynq, sustainable electronics, communication hardware.

### I. INTRODUCTION

The integration of green economy principles in FPGA technology aims to develop sustainable, energy-efficient circuits that reduce environmental impact. As FPGA circuits grow in complexity with an increasing number of transistors, managing static power consumption becomes essential. Techniques like power gating, clock gating, and voltage scaling help optimize standby power usage and battery life, making FPGAs more energy-efficient. Additionally, green computing promotes environmentally friendly design, manufacturing, and usage of electronic devices, reducing energy consumption and minimizing e-waste. Regulatory bodies such as the Bureau of Energy Efficiency monitor and certify energy-efficient appliances, encouraging manufacturers to adopt sustainable practices.

FPGAs, known for their programmable logic capabilities, are widely applied in AI, automotive, aerospace, telecommunications, and industrial

automation due to their high-speed parallel processing and low power requirements. Unlike traditional hardware, FPGAs can be reconfigured post-manufacturing, allowing for adaptable and modular designs that improve efficiency. They are programmed using hardware description languages (HDLs) like Verilog and VHDL, enabling customized logic circuit implementations.

One of the most fundamental components in digital computing is the Arithmetic Logic Unit (ALU), which performs essential arithmetic and logical operations. Adders, crucial for computation in CPUs and digital systems, significantly impact speed, power consumption, and area optimization. The 4-bit Full Adder, composed of multiple 2-bit full adders, improves digital circuit performance by minimizing excess transistor usage, reducing power dissipation, and enhancing overall computational efficiency. The ability to optimize these arithmetic units contributes to the development of

energy-efficient processors and high-performance computing architectures.

The continued advancement of FPGA-based energy-efficient digital systems will play a key role in sustainable computing, reducing energy consumption across industries while improving performance and adaptability. Future innovations will focus on AI-driven optimizations, adaptive power management, and machine learning-based resource allocation to further enhance efficiency and environmental sustainability.

## II. EXISTING METHOD

Traditional 4-bit full adder designs face significant challenges in terms of power consumption, thermal inefficiencies, and computational bottlenecks. These designs primarily rely on static CMOS logic and older FPGA architectures, which result in high static and dynamic power dissipation. The constant power requirement to maintain circuit states leads to excessive energy consumption, while frequent switching activities further increase dynamic power losses. Additionally, the sequential nature of traditional adders introduces high propagation delays, making them unsuitable for high-speed and energy-efficient applications.

Modern FPGA-based implementations address these limitations by integrating power-efficient transistors, clock gating, and optimized switching techniques. These improvements significantly reduce energy wastage and enhance computational efficiency. Moreover, dynamic voltage scaling and built-in temperature monitoring sensors in FPGA architectures, such as Spartan-7 and Zynq families, enable real-time thermal management. This prevents overheating, increases circuit longevity, and ensures stable operation under high-performance conditions. Unlike conventional designs that process data sequentially, FPGA-based adders leverage parallel processing capabilities, which significantly boosts execution speed and reduces computational delays. These enhancements make FPGA architectures ideal for high-speed applications in telecommunications, artificial intelligence (AI), and industrial automation.

Another major advantage of FPGA-based full adder circuits is their flexibility and scalability. Unlike rigid, fixed-function digital circuits, FPGAs allow real-time reconfiguration, making them adaptable for different computational tasks and design modifications. This adaptability is especially useful in prototyping and research, where frequent changes in circuit design are necessary to optimize performance. FPGA-based designs also offer modular scalability, enabling

designers to expand bit-widths or integrate additional functions with minimal hardware modifications.

To further improve power efficiency and computational speed, future FPGA-based full adder designs will focus on innovative low-power techniques. Emerging adiabatic logic and sub-threshold voltage operation can significantly reduce energy leakage and dynamic power dissipation. Additionally, the development of semiconductor materials like graphene and carbon nanotubes could further minimize resistive losses and enhance energy efficiency in digital circuits.

Another promising advancement involves AI-driven power management. By integrating machine learning (ML) and artificial intelligence (AI) algorithms, FPGA-based adders can dynamically optimize power consumption by predicting workload variations and adjusting circuit parameters in real time. This approach could lead to self-learning FPGA circuits that autonomously manage energy distribution, ensuring maximum efficiency under varying workloads.

Further technological improvements include advanced semiconductor technologies such as 3D-stacked ICs and quantum-dot transistors. These innovations will increase processing speed while maintaining low power consumption, making FPGA-based adders even more suitable for high-performance computing applications. Additionally, neuromorphic computing principles could be integrated into FPGA-based adders, mimicking brain-inspired energy-efficient computing models for even greater optimization.

Scalability and customization will continue to be key focus areas in FPGA development. Future designs may incorporate fault-tolerant and self-repairing circuits, ensuring greater reliability and longevity. FPGA-based full adders will be easily expandable to accommodate larger bit-widths, making them highly adaptable for a wide range of computational applications.

In summary, FPGA-based 4-bit full adders represent a major leap forward in digital circuit design, offering enhanced power efficiency, superior thermal management, and high-speed processing capabilities. As next-generation computing architectures continue to evolve, these energy-efficient FPGA solutions will play a pivotal role in applications spanning AI, quantum computing, and high-speed digital communication. By embracing cutting-edge semiconductor materials, AI-driven power management, and neuromorphic computing, FPGA technology is set to drive sustainable, high-performance digital computing in the future.

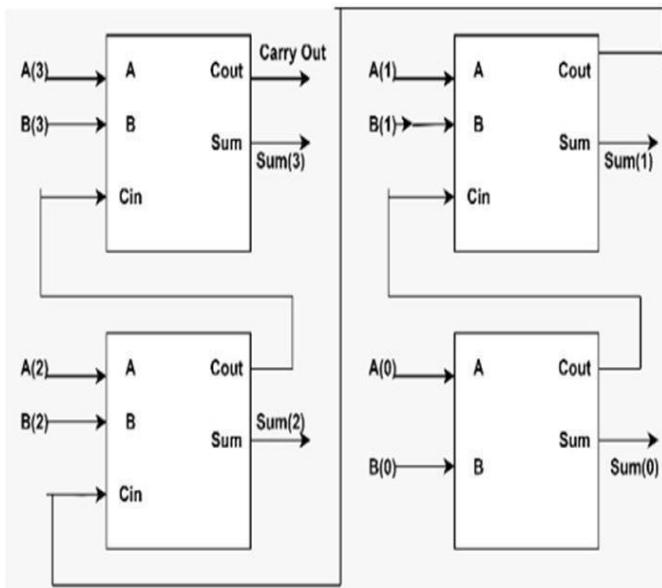

### Block diagram of 4-Bit full adder

By embracing cutting-edge semiconductor materials, AI-

Fig 1: The Block Diagram Of 4-Bit Full Adder

TABLE 1: Truth table of 4-Bit full adder

| Cin | A3 | A2 | A1 | A0 | B3 | B2 | B1 | B0 | S3 | S2 | S1 | S0 | Co |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0   | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  |

| 0   | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |

| 0   | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 0  |

| 0   | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |

| 0   | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 0  |

| 0   | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  |

| 0   | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  |

| 0   | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| 0   | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  |

| 0   | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  |

| 0   | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  |

| 0   | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

| 0   | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 1  |

| 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  |

| 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

$$Sum = A \oplus B \oplus C$$

$$Cout = AB + BCin + ACin$$

In summary, FPGA-based 4-bit full adders represent a major leap forward in digital circuit design, offering enhanced power efficiency, superior thermal management, and high-speed processing capabilities. As next-generation computing architectures continue to evolve, these energy-efficient FPGA solutions will play a pivotal role in applications spanning AI, quantum computing, and high-speed digital communication.

driven power management, and neuromorphic computing, FPGA technology is set to drive sustainable, high-performance digital computing in the future.

### III. PROPOSED METHOD

The proposed system aims to design an energy-efficient 4-bit full adder using modern FPGA architectures, specifically focusing on Zynq and Spartan-7 families. These FPGA platforms offer advanced features that enhance power efficiency, thermal stability, and high-speed performance, making them ideal for implementing optimized digital circuits. The motivation behind this design stems from the need to address challenges in power consumption, thermal dissipation, and processing speed, which are prevalent in traditional CMOS-based adders.

To achieve energy efficiency, the system incorporates dynamic voltage scaling (DVS) and power gating techniques that help minimize unnecessary power consumption during low-processing states. Additionally, clock gating is used to reduce switching activity, leading to lower dynamic power dissipation. These strategies collectively enhance circuit reliability and longevity, making the full adder suitable for power-sensitive applications.

Thermal management is another critical aspect of the design. Excessive heat generation in digital circuits can lead to performance degradation and potential component failure. To mitigate this, the proposed system integrates temperature monitoring sensors and adaptive cooling mechanisms that ensure the FPGA operates within safe temperature limits. By actively managing heat dissipation, the system maintains stable performance even under high computational loads.

The implementation process follows a structured approach, beginning with VHDL coding to define the logic of the 4-bit full adder. This is followed by functional and performance simulations to validate the correctness of the design. Once verified, the design is deployed on Zynq and Spartan-7 FPGA boards, where real-time power consumption and thermal performance measurements are conducted. The collected data is then compared with existing traditional designs to assess the improvements in efficiency, speed, and reliability.

The comparative analysis highlights the superiority of FPGA-based implementations over conventional CMOS-based adders. Unlike traditional designs that suffer from high power dissipation and sequential processing delays, FPGA-based adders leverage parallel processing capabilities to achieve faster computation with lower energy costs. Additionally, the ability to reconfigure FPGA logic dynamically allows for greater flexibility and scalability, making it possible to adapt the adder for higher-bit-width operations without significant design modifications.

Looking ahead, further optimizations in energy-efficient circuit design can be explored. Future advancements may include the integration of machine learning (ML) algorithms for dynamic power management, enabling real-time optimization based on workload variations. Additionally, emerging semiconductor technologies, such as graphene-based transistors and quantum-dot circuits, could provide groundbreaking solutions for ultra-low-power computing. The combination of AI-driven power control and next-generation materials has the potential to revolutionize FPGA-based arithmetic circuits, paving the way for more energy-efficient and high-performance computing systems.

The development of an energy-efficient 4-bit full adder using modern FPGA architectures, specifically Zynq and Spartan-7 families, demonstrates significant advancements in power optimization, thermal management, and computational efficiency. By incorporating dynamic voltage scaling, power gating, and clock optimization techniques, the proposed design effectively reduces energy consumption while maintaining high-speed performance. The integration of real-time temperature monitoring and adaptive cooling mechanisms ensures that thermal issues are mitigated, enhancing the reliability and lifespan of the circuit.

The results of this study highlight the superiority of FPGA-based implementations over traditional CMOS-based adders, particularly in terms of power efficiency, parallel processing, and scalability. The ability to dynamically reconfigure FPGA logic allows for flexible design modifications, making it suitable for future expansions and high-performance applications.

Looking forward, further research can explore the integration of machine learning algorithms for adaptive power management, as well as the adoption of emerging semiconductor materials to further minimize energy dissipation. With continuous advancements in low-

power FPGA technologies, this research lays the foundation for more efficient arithmetic circuits, contributing to the broader goal of sustainable and energy-conscious digital computing.

The proposed system focuses on designing an energy-efficient 4-bit full adder using modern FPGA architectures, specifically targeting the Zynq and Spartan-7 families. The key objectives of the design are to improve power efficiency, thermal management, and high-speed performance.

The methodology involves using Xilinx Vivado software for implementation while incorporating dynamic voltage scaling and power gating to optimize energy consumption. Thermal monitoring mechanisms will be implemented to maintain optimal operating temperatures, enhancing system reliability.

The implementation steps begin with VHDL coding of the full adder, followed by simulation to verify functionality and performance. The design is then deployed on Zynq and Spartan-7 FPGA boards, where power consumption and thermal characteristics are measured. Finally, a comparative analysis is conducted to assess improvements over traditional designs in terms of efficiency and performance.

TABLE 2: Comparison of Zynq and Spartan-7 Boards

| SL.NO | Feature                      | Zynq FPGAs                                                   | Spartan-7 FPGAs                             |

|-------|------------------------------|--------------------------------------------------------------|---------------------------------------------|

| 1     | <b>Processor Integration</b> | Integrates ARM Cortex-A9 processor with FPGA logic           | No processor integration (FPGA-only design) |

| 2     | <b>Flexibility</b>           | Combines software programmability with hardware acceleration | Offers hardware programmability only        |

| 3     | <b>Performance</b>           | Higher performance, suitable for complex tasks               | Optimized for simpler tasks                 |

| 4     | <b>Power Consumption</b>     | Higher due to the processor integration                      | Optimized for low-power use                 |

| 5     | <b>Cost</b>                  | More expensive due to added processing capability            | Budget-friendly for cost-efficient designs  |

|   |                            |                                                         |                                                           |

|---|----------------------------|---------------------------------------------------------|-----------------------------------------------------------|

| 6 | <b>Preferred Use Cases</b> | Industrial automation, robotics, and advanced computing | Automotive systems, IoT devices, and consumer electronics |

|---|----------------------------|---------------------------------------------------------|-----------------------------------------------------------|

#### IV. RESULTS AND DISCUSSION

##### Power Consumption Analysis

On the basis of clock frequency and switching activity, dynamic power consumption was examined. Low-power design methods were used to reduce static power, also known as leakage power.

##### Run Behavioural Simulation

1. In the Flow Navigator, go to Simulation → Run Simulation → Run Behavioural Simulation.

2. Wait for the Waveform Viewer to open. Process to launch the project in Xilinx Vivado

Step 1: Open an Existing Project

1. In the Vivado Start Page, click Open Project.

2. Navigate to the folder where your project is saved.

3. Select the.xpr (Vivado Project File) and click Open.

4. The project will load, showing

##### Run Synthesis

1. In the Flow Navigator, click Synthesis → Run Synthesis.

2. Vivado will convert your HDL code into a netlist.

3. Once synthesis completes, review any warnings or errors.

4. Click Open Synthesized Design to inspect the generated hardware structure.

##### Run Implementation

1. Click Implementation → Run Implementation in the Flow Navigator.

2. Vivado will perform placement and routing of the design.

3. Once completed, review timing reports to check for violations.

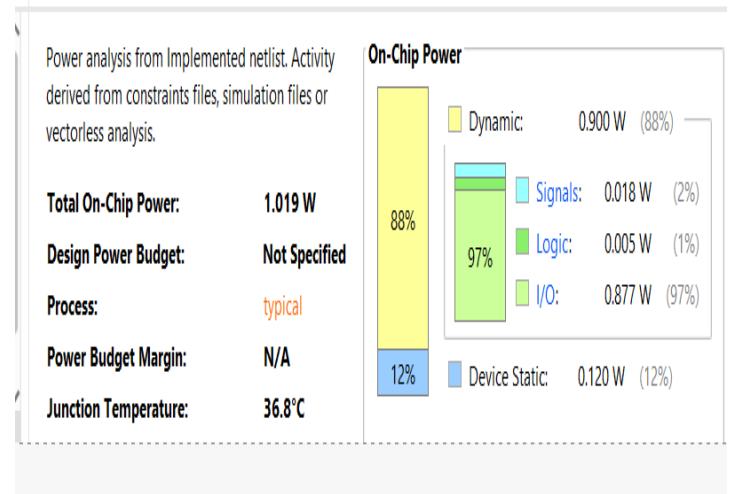

##### Power Consumption and Temperature Analysis of Zynq

When the circuit was implemented using a Spartan-7 board, we discovered that it used 1.019W of total chip power and had a temperature of 36.8 degrees Celsius and a thermal margin of 48.2 degrees Celsius per watt. 0.098W of static power and 0.900W of dynamic power are consumed. Fig. 2 displays the power consumed by the I/O, logic, and signal resources

Fig 2: The Power Consumption and Temperature Analysis of Zynq

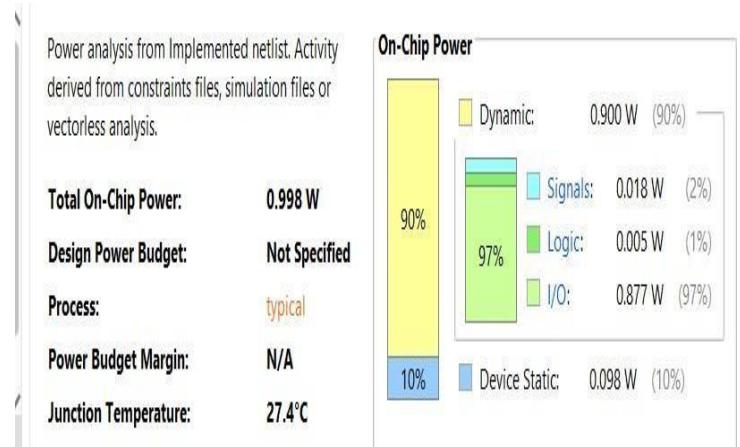

##### Power Consumption and Temperature Analysis of Spartan-7

When the circuit was implemented using a Spartan-7 board, we discovered that it used 0.998W of total chip power and had a temperature of 27.4 degrees Celsius and a thermal margin of 57.6 degrees Celsius per watt. 0.098W of static power and 0.900W of dynamic power are consumed. Fig. 3 displays the power consumed by the I/O, logic, and signal resources.

TABLE 3: Comparison Between Simulation Analysis of Zynq and Spartan-7

| Board name | Total on chip power (in watts) | Static power (in watts) | Dynamic power (in watts) | Junction Temperature (in degree Celsius) | Thermal Margin (in degree Celsius) |

|------------|--------------------------------|-------------------------|--------------------------|------------------------------------------|------------------------------------|

| Zynq       | 1.019                          | 0.12                    | 0.900                    | 36.8                                     | 48.2                               |

| Spartan-7  | 0.998                          | 0.900                   | 0.098                    | 27.4                                     | 57.6                               |

## V. CONCLUSION

In the course of this research, we employed Zynq and Spartan-7 boards to implement a 4-bit Full Adder while keeping an eye on hardware utilization, temperature, and power consumption. It is observed that 1.019 watts of power is consumed using the Zynq board, and 0.998 watts of power is consumed using the Spartan-7 board. Spartan-7's board consumes 97.94 percent less power than Zynq. Spartan-7's temperature is 27.4 degrees Celsius, the lowest when compared to Zynq's 36.8 degrees Celsius. The Spartan-7 Board is able to successfully maintain temperature and energy at the end of the experiment.

## VI. REFERENCES

[1] A. Shrivastava et al., "VLSI Implementation of Green Computing Control Unit on Zynq FPGA for Green Communication," Wireless Communications and Mobile Computing, vol. 2021, pp. 1–10, Nov. 2021.

[2] Toutanova.,& Marinova, G. Telecommunication system for green economy-a survey. Electrotechnica & Electronica (E+ E), vol. 52, pp. 10-16, 2017.

[3] <https://www.cseindia.org/energy-efficient-appliances-2000> accessed on February 02, 2024, at 11:00 hrs.

[4] J. Serrano, "Introduction to FPGA design," CERN Document Server, pp. 231-247, 2008.

[5] V. Bhardwaj, A. Kaur, K. R. Ramkumar, S. Mittal and B. Singh, "Design of an Energy Efficient Serial Communication Device using FPGA," 2023 International Conference on Disruptive Technologies (ICDT), Greater Noida, India, pp. 386- 389, 2023.

[6] S. Mittal and K. R. Ramkumar, "Different Communication Technologies and Challenges for implementing Under Water Sensor Network," 2021 12th International Conference on Computing Communication and Networking Technologies (ICCCNT), Kharagpur, India, pp. 01-16, 2021.

[7] B. Koyada, N. Meghana, M. O. Jaleel and P. R. Jeripotula, "A comparative study on adders," 2017 International Conference on Wireless Communications, Signal Processing and Networking (WiSPNET), Chennai, India, pp. 2226- 2230, 2017.

[8] P. Martha, N. Kajal, P. Kumari and R. Rahul, "An efficient way of implementing high speed 4-Bit advanced multipliers in FPGA," 2018 2nd International Conference on Electronics, Materials Engineering & Nano-Technology (IEMENTech), Kolkata, India, pp. 1-5, 2018.

[9] G. Dhanabalan, V. Karutharaja and M. Sakthimohan, "Realization of Resource Efficient Block RAM Based Eight Bit Adder in FPGA," 2019 IEEE International Conference on Intelligent Techniques in Control, Optimization and Signal Processing (INCOS), Tamilnadu, India, pp. 1- 5, 2019.

[10] V. Thamizharasan and N. Kasthuri, "High- Speed Hybrid Multiplier Design Using a Hybrid Adder with FPGA Implementation," IETE Journal of Research, pp. 1-9, Apr. 2021.

[11] P. Radhakrishnan, G. Themozhi, FPGA implementation of XOR-MUX full adder-based DWT for signal processing applications, Microprocessors and Microsystems, Volume 73, 102961, ISSN 0141-9331, 2020.

[12] S. Mittal and K. R. Ramkumar, "Comparative evaluation of fully homomorphic encryption algorithms in cloud environment," Int. J. Electron. Secur. Digit. Forensics, vol. 15, no. 4, pp. 333–347, 2023.

[13] L. A. Ajao, M. A. Adegbeye, J. Agajo, A. O. Ajao, and A. A. Yunus, "FPGA Logic Circuit Implementation and Synthesis with VHDL Programming: A Learning Approach", ijesc, vol. 2, no. '1, pp. 1–11, Nov. 2017.

[14] S. Hashemi, M. Rahimi Azghadi, and K. Navi, "Design and analysis of efficient QCA reversible adders," The Journal of Supercomputing, vol. 75, no. 4, pp. 2106–2125, Nov. 2018.

[15] P. Datta, S. N. Panda, S. Tanwar and R. K. Kaushal, "A Technical Review Report on Cyber Crimes in India," 2020 International Conference on Emerging Smart Computing and Informatics (ESCI), Pune, India, pp. 269-275, 2020.